## Парамонов В.Ю.

Научный руководитель к.т.н., асс. Докторов А.Н.

Муромский институт (филиал) федерального государственного образовательного учреждения высшего образования «Владимирский государственный университет имени Александра Григорьевича и Николая Григорьевича Столетовых» 602264, г. Муром, Владимирская обл., ул. Орловская, 23 E-mail: andreybolshev2@yandex.ru, doctorov\_a\_n@mail.ru

## Исследование интерфейсов управления цифровыми вычислительными синтезаторами

В технике формирования радиосигналов нашли широкое применение цифровые вычислительные синтезаторы (ЦВС). Преимущества их малой потребляемой мощности, низкой стоимости и интегрального исполнения, с возможностью цифрового программирования (и перепрограммирования) формы выходного сигнала делают данные устройства цифрового синтеза сигналов более предпочтительными, чем устройства на дискретных элементах. Поскольку цифровые вычислительные синтезаторы программируется цифровым способом, фазу и частоту сигнала можно легко перестраивать в режиме реального времени [1, 2], при этом нет необходимости изменения параметров внешних компонентов – катушек индуктивности и конденсаторов. Выходной аналоговый сигнал ЦВС образуется из базового тактового сигнала, представляющего собой меандр, путем цифровых преобразований. Этот метод называется методом прямого цифрового синтеза На выходе цифрового синтезатора имеется ЦАП – цифроаналоговый преобразователь, преобразующий полученный в результате вычислений цифровой сигнал в аналоговую форму.

Цифровой вычислительный синтезатор представляет собой устройство, управляемое электронной вычислительной машиной или микроконтроллером [3]. С помощью микроконтроллеров можно управлять ЦВС, как посредством последовательного интерфейса SPI (Serial Peripheral Interface — последовательный периферийный интерфейс), так и параллельным способом.

Рассмотрим в качестве примера способы управления микросхемой цифрового вычислительного синтезатора, производства компании Analog Devices - AD9850 [4]. Данная микросхема синтезатора частот содержит 40-битный регистр, который используется для программирования. Он включает в себя 32-битное слово управления частотой, 5-битное слово фазовой модуляции, и функцию отключения питания. Этот регистр может быть загружен в параллельном или последовательном режиме [5].

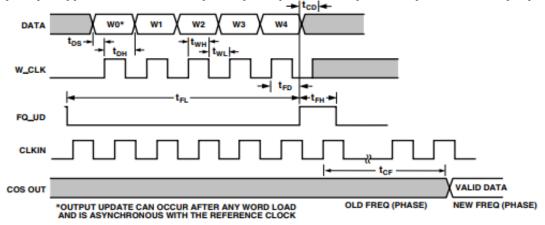

Пример загрузки кода частоты в регистр в параллельном режиме представлен на рисунке 1.

Рис. 1 Параллельная загрузка.

В режиме параллельной загрузки регистр загружается через 8-битную шину данных. Полное 40-битное слово требует пяти итераций загрузки 8-битного слова. Сигналы W\_CLK и FQ\_UD используются для адресации и загрузки в регистры. Нарастающий фронт FQ\_UD загружает (до) 40-бит управляющее слово данных (data-word) в устройство, после чего сбрасывает адресный указатель в первый регистр. Последующие передние фронты W\_CLK

загружают 8-битные данные, по словам [7: 0] и смещают адресный указатель на следующий регистр[5]. После пяти загрузок сигналы на контакте микросхемы W\_CLK игнорируются, по сбросу или нарастанию фронта на FQ UD сбрасывает адресный указатель на первый регистр.

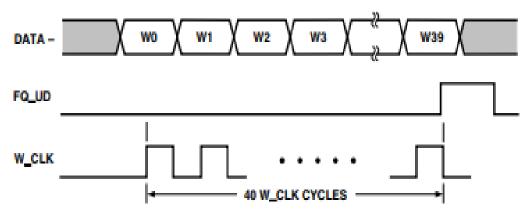

В режиме последовательной загрузки, рассмотренном на рисунке 2, который осуществляется через последовательный периферийный интерфейс, по каждому нарастанию фронта кварцевого генератора тактовой частоты W\_CLK на контакте микросхемы цифрового вычислительного синтезатора 25 (D7) поступают 1-битные данные кода частоты. После сдвига 40 битов данных кода частоты на контакт FQ\_UD необходимо подать импульс для обновления выходной частоты (или фазы). [5]

Рис. 2. Последовательная загрузка.

Таким образом, для управления цифровыми вычислительными синтезаторами могут применяться два способа управления — последовательный и параллельный. Последовательный метод может быть использован для цифровых вычислительных синтезаторов в миниатюрном исполнении. Параллельный способ управления применяется, если к устройству управления предъявляются высокие требования по быстродействию, и отсутствуют особые требований к размерам микросхемы. В дальнейшем, на основе результатов проведенной работы по исследованию интерфейсов управления будет создан экспериментальный стенд, позволяющий управлять несколькими цифровыми вычислительными синтезаторами.

## Литература

- 1. Murphy E. Slattery C. Ask The Application Engineer 33 All About Direct Digital Synthesis / Eva Murphy Colm Slattery // Analog Dialogue. 2004. August 38-08.

- 2. Technical Tutorial on Digital Signal Synthesis. 1999, Analog Devices, Inc.

- 3. Суржик Д.И Алгоритмы формирования управляющих сигналов автокомпенсаторов фазовых искажений цифровых вычислительных синтезаторов и устройств на их основе / Суржик Д.И., Курилов И.А., Васильев Г.С., Харчук, С.М. // Алгоритмы, методы и системы обработки данных, сер. ОТ. 2017. Выпуск 2. С. 129-135

- 4. Цифровые синтезаторы сигналов (DDS) и модуляторы [Электронный ресурс]: сайт фирмы Analog Devices, Inc., 2013. URL: <a href="http://www.analog.com/ru/rfif-components/direct-digital-synthesis-dds/products/index.html">http://www.analog.com/ru/rfif-components/direct-digital-synthesis-dds/products/index.html</a>

- 5. Direct Digital Synthesizer AD9850 // https://www.analog.com/ru/products/ad9850.html#product-documentation